两位加法器设计,两位加法器逻辑图

作者:admin 发布时间:2024-03-29 18:00 分类:资讯 浏览:20 评论:0

全加器的逻辑功能

1、一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。常用二进制四位全加器74LS283。

2、全加器的逻辑功能是两个同位的二进制数及来自低位的进位三者相加。全加器用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。

3、计算本位加法的进位,将G和上一位的进位C0相加得到C4,即为本位加法的进位。得到四位二进制数的相加和S3S2S1S0和最高位的进位C4,作为输出。

4、首先,将四个输入位和进位位相加,得到一个中间结果。其次,对于中间结果的每一位,可以用异或门的逻辑电路实现。

5、一位全加器(FA)的逻辑表达式为:S=A⊕B⊕Cin;Cout=AB+BCin+ACin,其中A,B为要相加的数,Cin为进位输入;S为和,Co是进位输出;如果要实现多位加法可以进行级联,就是串起来使用。

6、全加器逻辑图:二进制全加器 用于门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。

什么是一位全加器

1、全加器是能够计算低位进位的二进制加法电路。相加时不考虑进位的二进制加法则称为半加,所用的电路叫做半加器。相加时考虑来自低位的进位以及向高位的进位的二进制加法则称为全加,所用的电路叫做全加器。

2、是指:两个一位 二进制数 带有进位的 加法器 。二进制表示中只有0和1。比如设:两个加数A和B,低位的进位是C,和为S,进位是Cin,则{Cin,S}=A+B+C。

3、全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。

4、一位全加器的表达式如下:Si=Ai⊕Bi⊕Ci-1 第二个表达式也可用一个异或门来代替或门对其中两个输入信号进行求和:其中Ai为被加数,Bi为加数,相邻低位来的进位数为Ci-1,输出本位和为Si。向相邻高位进位数为Ci。

设计一个加法器?

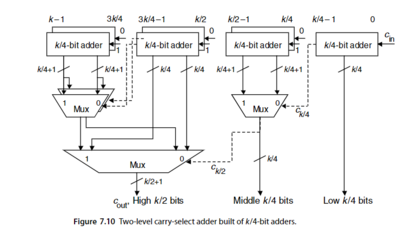

1、因此将这种结构的电路称为串行进位加法器。并行进位加法器:特点:可以通过逻辑电路实现得出每一位全加器的进位输入信号,无需再从最低位开始向高位逐位传递进位信号,优势在于提高了运行速度。

2、用JK触发器设计一个三进制计数器,计数为00,01,10三个状态的循环,所以需要用到两个JK触发器。先将2个JK触发器接成同步4进制加法计数器,再改成3进制加法器。

3、一位全加器的真值表,其中Ai为被加数,Bi为加数,相邻低位来的进位数为Ci-1,输出本位和为Si。

4、来自电子科技大学中山学院(数电实验)基础实验 (1)利用7483设计4位以内的加法器,请给出实验电路,并根据表4要求填写输出结果。(2)给出7485实现4位二进制比较器的电路图,分析其工作原理。

5、该半加法器采用异或门(74LS86)和双非门、双片74LS00和双非门实现。最基本的逻辑关系是和、或、和,而最基本的逻辑门是和、或门与非门。逻辑门可以由电阻、电容、二极管、三极管等分立元件组成。

数字电路请用维持阻塞D触发器设计一个二位二进制加法计数器,写出方程...

最佳答案 该设计主要思路为时钟分频和逻辑运算。也可以理解为计数器设计和进位提取。

选用芯片74LS74,管脚图如下。说明:74LS74是上升沿触发的双D触发器, D触发器的特性方程为 设计方案:用触发器组成计数器。触发器具有0 和1两种状态,因此用一个触发器就可以表示一位二进制数。

由于CP1取自Q0,所以在Q0的下降沿触发下,FF1的输出Q1要翻转。同理,由于CP2=Q1,所以在Q1的下降沿触发下,FF2的输出Q2要翻转。

可以。对N个D触发器组成的级联结构的最后输出Q或者Q非的高电平(计1)或者低电平(计0)进行计数,即可以实现计数器的功能。例如时钟源的频率是100HZ,则最终输出端就会以100/2的N次方 的频率进行计数。

LS74是双D触发器,组两位异步加法计数器很简单,每个D触发器先构成一位计数器,然后Q0非输出端作D1的CP脉冲,逻辑图如下图所示。

画出全加器逻辑图并给出进位公式

1、多个一位全加器进行级联可以得到多位全加器。常用二进制四位全加器74LS283。提供与非门的是74LS86,有4个与非门。

2、其中,一位全加器(FA)的逻辑表达式为:S=A⊕B⊕Cin Co=(A⊕B)Cin+AB 其中A、B为要相加的数,Cin为进位输入;S为和,Co是进位输出。

3、一位全加器(FA)的逻辑表达式为:S=A⊕B⊕Cin,Co=AB+BCin+ACin,其中A,B为要相加的数,Cin为进位输入,S为和,Co是进位输出。

4、在其它位,都是三个一位数相加,同样会产生 C(进位)以及 S(和)。三个一位数相加,这就必须用“全加器”完成了。它们的真值表以及逻辑表达式,在图中,都已给出。它们的逻辑电路图,当然也可以用“门电路”组成。

5、Y为全加器的和S,2Y为全加器的高位进位C1,于是就可以令数据选择器的输入为:A1=A,A0=B,1DO=1D3=C0,1D1=1D2=C0反,2D0=0,2D3=1,2D1=2D2=C0,1Q=S1,2Q=C1;根据对应的管脚连接电路。

6、见下图 追问: 看不见图!郁闷! 全加器 的 逻辑 式为: 它有三个 输入变量 ,加数A和B以及低位的进位信号C0,所以选用一个ROM,确定三个 地址线 ,分别代表A、B和C0。

如何用74HC153设计两位全加器?

1、当x为1时,下边的译码器打开,上边的译码器输出高阻抗。译码输出高4位(yz组合)。

2、具体如下图:其中,一位全加器(FA)的逻辑表达式为:S=A⊕B⊕Cin Co=(A⊕B)Cin+AB 其中A、B为要相加的数,Cin为进位输入;S为和,Co是进位输出。

3、HC153是一颗双路的四输入选通器(模拟开关)。所以,应该说它的功能是从四对输入数据中选择某一对并输出。

4、位二进制全减法器电路由数据选择器74ls153和门电路实现,需要真值表和电路图。逻辑函数,写成最小项表达式:Y=m1+m2+m4+m7 Cy=m1+m2+m3+m7 1位二进制全减器电路真值表和逻辑图,也就是模拟图如下。

5、真值表:ABC L1L2 000 0 0 001 1 0 010 1 0 011 0 1 100 1 0 101 0 1 110 0 1 111 1 1 ABC接全加器输入端,L1,L2就是全加器的本位输出和进位输出。

6、一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。常用二进制四位全加器74LS283。

相关推荐

欢迎 你 发表评论:

- 资讯排行

- 标签列表

- 友情链接